AXI协议

AXI协议特点

- 高性能、高带宽、低延迟的片内总线

- 总线的地址/控制和数据通道是分离的

- 支持不对齐的数据传输

- 支持突发传输,突发传输过程中只需要首地址

- 具有分离的读/写数据通道

- 支持显著传输访问和乱序访问

- 更加容易进行时序收敛

AXI协议的接口

AXI4:高性能存储映射接口(存储映射(Meamory Map):如果一个协议是存储映射的,那么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表明是针对该存储空间的读写操作)

AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信(AXI-Lite为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器)

AXI4-Stream:用于高速数据流传输,非存储映射接口(AXI-Stream 接口则像 FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、PCIe、DMA 接口等需要高速数据传输的场合。

)

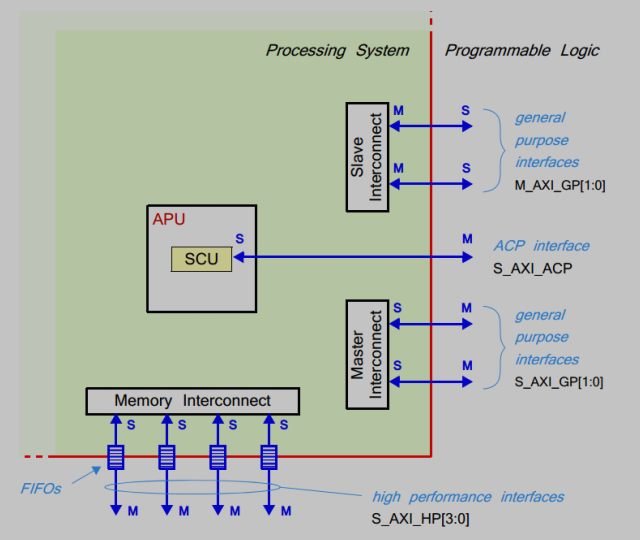

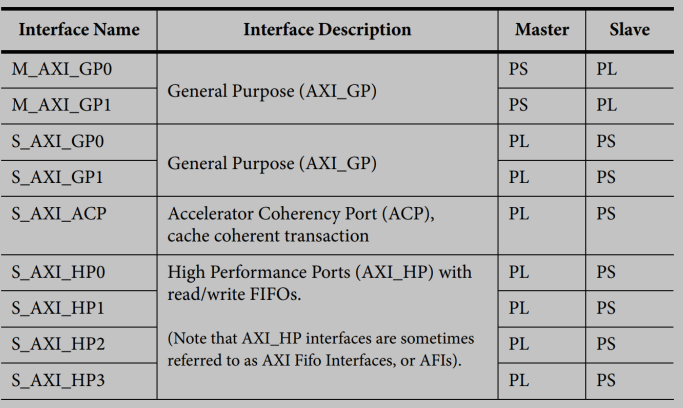

PS与PL之间的AXI接口

PS 和 PL 之间的 9 个 AXI 接口可以分成三种类型

通用 AXI:一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。四个接口:两个 PS 做主机,另两个 PL 做主机。

加速器一致性端口:在 PL 和 APU 内的 SCU 之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL 的单元之间的一致性。PL 是做主机。

高性能端口:四个高性能 AXI 接口,带有 FIFO 缓冲来提供“批量”读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中 PL 都是做主机。

(后续将更新AXI协议实践部分内容……)

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Tadeo's Blog!